## **JYJE9121**

## 1-220 MHz High Performance Differential Oscillator

#### **Features**

- Any frequency between 1 MHz and 220 MHz accurate to 6 decimal places

- LVPECL and LVDS output signaling types

- 0.6ps RMS phase jitter (random) over 12 kHz to 20 MHz bandwidth

- Frequency stability as low as ±10 ppm

- Industrial and extended commercial temperature ranges

- Industry-standard packages: 3.2x2.5, 5.0x3.2 and 7.0x5.0 mmxmm

- For frequencies higher than 220 MHz, refer to JYJE9122 datasheet

## **Applications**

- 10GB Ethernet, SONET, SATA, SAS, Fibre Channel, PCI-Express

- Telecom, networking, instrumentation, storage, servers

#### **Electrical Characteristics**

| Parameter and Conditions                           | Symbol    | Min.    | Тур.     | Max.       | Unit       | Condition                                                             |  |  |

|----------------------------------------------------|-----------|---------|----------|------------|------------|-----------------------------------------------------------------------|--|--|

| LVPECL and LVDS, Common Electrical Characteristics |           |         |          |            |            |                                                                       |  |  |

| Supply Voltage                                     | Vdd       | 2.97    | 3.3      | 3.63       | V          |                                                                       |  |  |

|                                                    |           | 2.25    | 2.5      | 2.75       | V          |                                                                       |  |  |

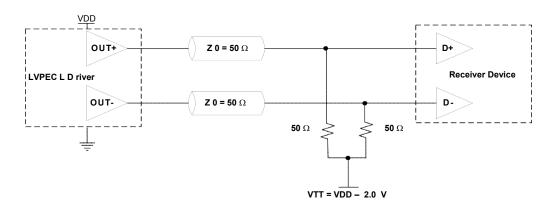

|                                                    |           | 2.25    | _        | 3.63       | V          | Termination schemes in Figures 1 and 2 - XX ordering code             |  |  |

| Output Frequency Range                             | f         | 1       | -        | 220        | MHz        |                                                                       |  |  |

| Frequency Stability                                | F_stab    | -10     | -        | +10        | ppm        |                                                                       |  |  |

|                                                    |           | -20     | -        | +20        | ppm        | Inclusive of initial tolerance, operating temperature, rated power    |  |  |

|                                                    |           | -25     | -        | +25        | ppm        | supply voltage, and load variations                                   |  |  |

|                                                    |           | -50     | -        | +50        | ppm        | 1                                                                     |  |  |

| First Year Aging                                   | F_aging1  | -2      | -        | +2         | ppm        | 25°C                                                                  |  |  |

| 10-year Aging                                      | F_aging10 | -5      | -        | +5         | ppm        | 25°C                                                                  |  |  |

| Operating Temperature Range                        | T_use     | -40     | -        | +85        | °C         | Industrial                                                            |  |  |

|                                                    |           | -20     | -        | +70        | °C         | Extended Commercial                                                   |  |  |

| Input Voltage High                                 | VIH       | 70%     | -        | _          | Vdd        | Pin 1, OE or ST                                                       |  |  |

| Input Voltage Low                                  | VIL       | _       |          | 30%        | Vdd        | Pin 1. OE or ST                                                       |  |  |

| Input Pull-up Impedance                            | Z in      | _       | 100      | 250        | kΩ         | Pin 1, OE logic high or logic low, or ST logic high                   |  |  |

|                                                    | _         | 2       | -        | _          |            |                                                                       |  |  |

| Start-up Time                                      | Totart    |         |          |            | ΜΩ         | Pin 1, ST logic low                                                   |  |  |

| Start-up Time                                      | T_start   | -       | 6        | 10         | ms         | Measured from the time Vdd reaches its rated minimum value.           |  |  |

| Resume Time                                        | T_resume  | -       | 6        | 10         | ms         | In Standby mode, measured from the time ST pin crosses 50% threshold. |  |  |

| Duty Cycle                                         | DC        | 45      | -        | 55         | %          | Contact JYJE for tighter dutycycle                                    |  |  |

|                                                    |           | L       | VPECL, D | C and AC ( | Character  | istics                                                                |  |  |

| Current Consumption                                | ldd       | -       | 61       | 69         | mA         | Excluding Load Termination Current, Vdd = 3.3V or 2.5V                |  |  |

| OE Disable Supply Current                          | I_OE      | _       | -        | 35         | mA         | OE = Low                                                              |  |  |

| Output Disable Leakage Current                     | I_leak    | _       | -        | 1          | μΑ         | OE = Low                                                              |  |  |

| Standby Current                                    | I_std     | -       |          | 100        | μΑ         | ST = Low, for all Vdds                                                |  |  |

| Maximum Output Current                             | I_driver  | _       | _        | 30         | mA         | Maximum average current drawn from OUT+ or OUT-                       |  |  |

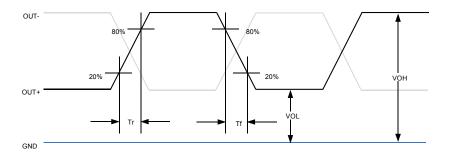

| Output High Voltage                                | VOH       | Vdd-1.1 | _        | Vdd-0.7    | V          | See Figure 1(a)                                                       |  |  |

| Output Low Voltage                                 | VOL       | Vdd-1.9 | _        | Vdd-1.5    | V          | See Figure 1(a)                                                       |  |  |

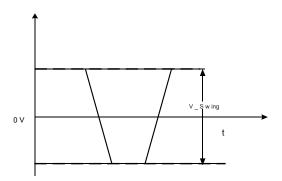

| Output Differential Voltage Swing                  | V_Swing   | 1.2     | 1.6      | 2.0        | V          | See Figure 1(b)                                                       |  |  |

| Rise/Fall Time                                     | Tr, Tf    | _       | 300      | 700        | ps         | 20% to 80%, see Figure 1(a)                                           |  |  |

| OE Enable/Disable Time                             | T_oe      | _       | -        | 115        | ns         | f = 212.5 MHz - For other frequencies, T_oe = 100ns + 3 period        |  |  |

| RMS Period Jitter                                  | T_jitt    | -       | 1.2      | 1.7        | ps         | f = 100 MHz, VDD = 3.3V or 2.5V                                       |  |  |

|                                                    |           | -       | 1.2      | 1.7        | ps         | f = 156.25 MHz, VDD = 3.3V or 2.5V                                    |  |  |

| DMO Dhasa littan (namala 11)                       | T         | -       | 1.2      | 1.7        | ps         | f = 212.5 MHz, VDD = 3.3V or 2.5V                                     |  |  |

| RMS Phase Jitter (random)                          | T_phj     | -       | 0.6      | 0.85       | ps         | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdds    |  |  |

|                                                    |           |         | LVDS, DC | and AC Cl  | naracteris | stics                                                                 |  |  |

| Current Consumption                                | ldd       | -       | 47       | 55         | mA         | Excluding Load Termination Current, Vdd = 3.3V or 2.5V                |  |  |

| OE Disable Supply Current                          | I_OE      | -       | -        | 35         | mA         | OE = Low                                                              |  |  |

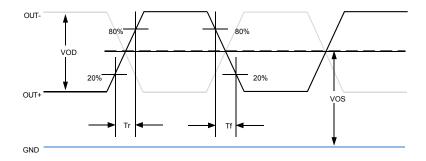

| Differential Output Voltage                        | VOD       | 250     | 350      | 450        | mV         | See Figure 2                                                          |  |  |

Rev. 1.07 Page 1 of 8

## **JYJE9121**

## 1-220 MHz High Performance Differential Oscillator

## Electrical Characteristics(continued)

| Parameter and Conditions                    | Symbol | Min.  | Тур. | Max.  | Unit | Condition                                                          |  |

|---------------------------------------------|--------|-------|------|-------|------|--------------------------------------------------------------------|--|

| LVDS, DC and AC Characteristics (continued) |        |       |      |       |      |                                                                    |  |

| Output Disable Leakage Current              | I_leak | -     | -    | 1     | μА   | OE = Low                                                           |  |

| Standby Current                             | I_std  | -     | -    | 100   | μА   | ST = Low, for all Vdds                                             |  |

| VOD Magnitude Change                        | ΔVOD   | -     | -    | 50    | mV   | See Figure 2                                                       |  |

| Offset Voltage                              | VOS    | 1.125 | 1.2  | 1.375 | V    | See Figure 2                                                       |  |

| VOS Magnitude Change                        | ΔVOS   | -     | -    | 50    | mV   | See Figure 2                                                       |  |

| Rise/Fall Time                              | Tr, Tf | _     | 495  | 700   | ps   | 20% to 80%, see Figure 2                                           |  |

| OE Enable/Disable Time                      | T_oe   | _     | -    | 115   | ns   | f = 212.5 MHz - For other frequencies, T_oe = 100ns + 3 period     |  |

| RMS Period Jitter                           | T_jitt | -     | 1.2  | 1.7   | ps   | f = 100 MHz, VDD = 3.3V or 2.5V                                    |  |

|                                             |        | -     | 1.2  | 1.7   | ps   | f = 156.25 MHz, VDD = 3.3V or 2.5V                                 |  |

|                                             |        | _     | 1.2  | 1.7   | ps   | f = 212.5 MHz, VDD = 3.3V or 2.5V                                  |  |

| RMS Phase Jitter (random)                   | T_phj  | _     | 0.6  | 0.85  | ps   | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdds |  |

### **Pin Description**

| Pin | Мар  | Functionality |                                                                                                      |  |  |  |  |

|-----|------|---------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | OE   | Input         | H or Open: specified frequency output<br>L: output is high impedance                                 |  |  |  |  |

| 1   | ST   | Input         | H or Open: specified frequency output L: Device goes to sleep mode. Supply current reduces to I_std. |  |  |  |  |

| 2   | NC   | NA            | No Connect; Leave it floating or connect to GND for better heat dissipation                          |  |  |  |  |

| 3   | GND  | Power         | VDD Power Supply Ground                                                                              |  |  |  |  |

| 4   | OUT+ | Output        | Oscillator output                                                                                    |  |  |  |  |

| 5   | OUT- | Output        | Complementary oscillator output                                                                      |  |  |  |  |

| 6   | VDD  | Power         | Power supply voltage                                                                                 |  |  |  |  |

#### **Absolute Maximum**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Min. | Max. | Unit |

|----------------------------------------------------------------------|------|------|------|

| Storage Temperature                                                  | -65  | 150  | °C   |

| VDD                                                                  | -0.5 | 4    | V    |

| Electrostatic Discharge (HBM)                                        | -    | 2000 | V    |

| Soldering Temperature (follow standard Pb free soldering guidelines) | -    | 260  | °C   |

### **Thermal Consideration**

| Package     | θJA, 4 Layer Board<br>(°C/W) | θJC, Bottom<br>(°C/W) |

|-------------|------------------------------|-----------------------|

| 7050, 6-pin | 142                          | 27                    |

| 5032, 6-pin | 97                           | 20                    |

| 3225, 6-pin | 109                          | 20                    |

#### **Environmental Compliance**

| Parameter                   | Condition/Test Method    |

|-----------------------------|--------------------------|

| Mechanical Shock            | MIL-STD-883F, Method2002 |

| Mechanical Vibration        | MIL-STD-883F, Method2007 |

| Temperature Cycle           | JESD22, Method A104      |

| Solderability               | MIL-STD-883F, Method2003 |

| Moisture SenJYJEivity Level | MSL1 @ 260°C             |

Rev. 1.07 Page 2 of 8

## **Waveform Diagrams**

Figure 1(a). LVPECL Voltage Levels per Differential Pin (OUT+/OUT-)

Figure 1(b). LVPECL Voltage Levels Across Differential Pair

Figure 2. LVDS Voltage Levels per Differential Pin (OUT+/OUT-)

Rev. 1.07 Page 3 of 8

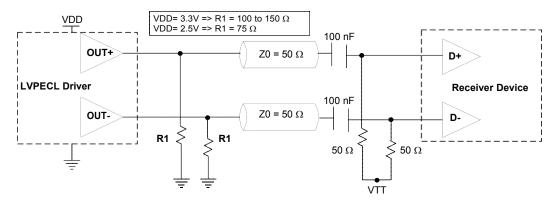

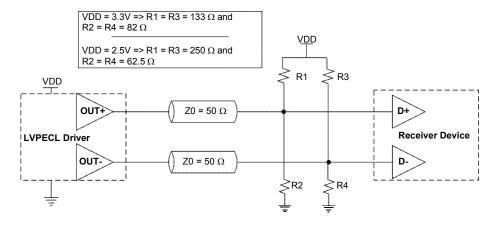

## **Termination Diagrams**

#### LVPECL:

Figure 3. LVPECL Typical Termination

Figure 4. LVPECL AC Coupled Termination

Figure 5. LVPECL with Thevenin Typical Termination

Rev. 1.07 Page 4 of 8

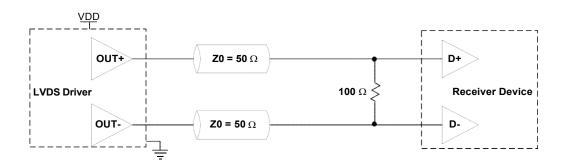

### LVDS:

Figure 6. LVDS Single Termination (Load Terminated)

Rev. 1.07 Page 5 of 8

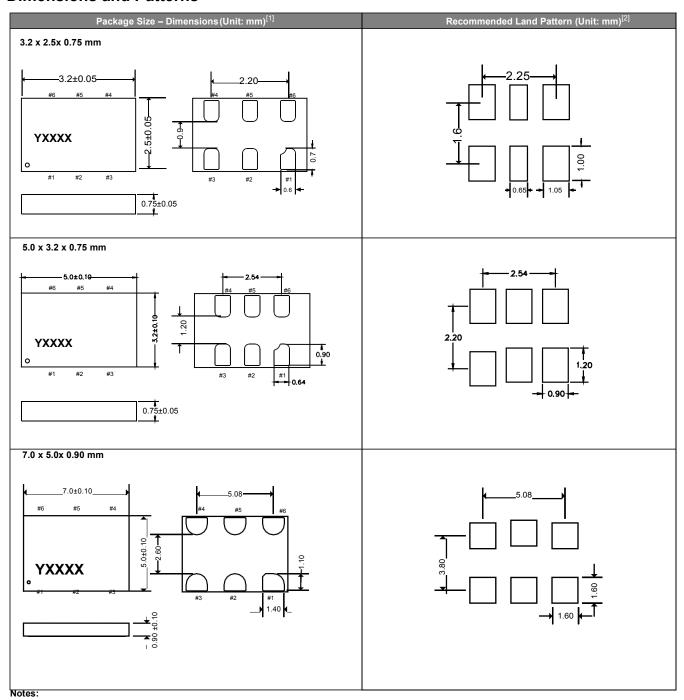

#### **Dimensions and Patterns**

- 1. Top Marking: Y denotes manufacturing origin and XXXX denotes manufacturing lot number. The value of "Y" will depend on the assembly location of the device.

- 2. A capacitor of value 0.1  $\mu\text{F}$  between Vdd and GND is recommended.

Rev. 1.07 Page 6 of 8

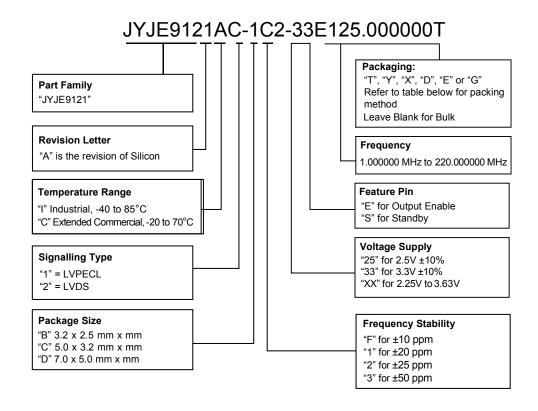

### **Ordering Information**

### **Ordering Codes for Supported Tape & Reel Packing Method**

| Device Size  | 8 mm T&R<br>(3ku) | 8 mm T&R<br>(1ku) | 8 mm T&R<br>(250u) | 12 mm T&R<br>(3ku) | 12 mm T&R<br>(1ku) | 12 mm T&R<br>(250u) | 16 mm T&R<br>(3ku) | 16 mm T&R<br>(1ku) | 16 mm T&R<br>(250u) |

|--------------|-------------------|-------------------|--------------------|--------------------|--------------------|---------------------|--------------------|--------------------|---------------------|

| 7.0 x 5.0 mm | _                 | _                 | _                  | _                  | _                  | _                   | Т                  | Υ                  | X                   |

| 5.0 x 3.2 mm | _                 | _                 | _                  | Т                  | Y                  | Х                   | _                  | _                  | _                   |

| 3.2 x 2.5 mm | D                 | Е                 | G                  | Т                  | Y                  | Х                   | -                  | -                  | -                   |

### **Frequencies Not Supported**

Range 1: From 209.000001 MHz to 210.999999 MHz

Rev. 1.07 Page 7 of 8

## **JYJE9121**

# 1-220 MHz High Performance Differential Oscillator

## **Revision History**

| Version | Release Date | Change Summary                                                            |

|---------|--------------|---------------------------------------------------------------------------|

| 1.01    | 2/20/13      | Original                                                                  |

| 1.02    | 12/3/13      | Added input specifications, LVPECL/LVDS waveforms, packaging T&Roptions   |

| 1.03    | 2/6/14       | Added 8mm T&R option and ±10 ppm                                          |

| 1.04    | 4/8/14       | Included 1.8V option for LVDS output only                                 |

| 1.05    | 7/30/14      | Included Thermal Consideration table                                      |

| 1.06    | 10/20/14     | Modified Thermal Consideration values. Preliminary removed from the title |

| 1.07    | 1/4/16       | Removed 1.8V option                                                       |

**Disclaimer:** This document is not an official JYJE datasheet. It is exported from a Master FrameMaker document for your convenience, to simplify the generation of your datasheet. The information in the official JYJE datasheet on JYJE's webJYJEe will be the final reference in case of conflicting information.

Rev. 1.07 Page 8 of 8